Field Programmable Gate Arrays and Applications

Chapter 2

Field Programmable Gate Arrays and Applications ( FPGA )

2.1 Introduction to FPGA:

Order custom essay Field Programmable Gate Arrays and Applications with free plagiarism report

450+ experts on 30 subjects

450+ experts on 30 subjects

Starting from 3 hours delivery

Starting from 3 hours delivery

A FPGA is a device that holds a lattice of reconfigurable entryway exhibit logic hardware. At the point when a FPGA is arranged, the inner hardware is joined in a mode that makes adjustments executing of the merchandise proviso. Dissimilar to processors, FPGAs usage committed equipment for managing logic and do n't hold a on the job model. FPGAs are truly parallel in nature so typical transforming operations do n't necessitate to seek the same assets. Therefore, the executing of one some piece of the proviso is non influenced when excess preparing is included. Additionally, different control circles can run on a lone FPGA appliance at typical rates. FPGA-based control models can authorise basic interlock logicand could be intended to debar I/O drive by an decision maker. Nonetheless, dissimilar to hard-wired printed circuit board ( PCB ) plans which have altered equipment assets, FPGA-based models can really rewire their interior hardware to allow reconfiguration after the control model is sent to the field. FPGA appliances convey the executing and dependableness of devoted equipment hardware.

A individual FPGA can replace many distinct sections by consolidating a big figure of logicentryways in a lone coordinated circuit ( IC ) bit. The interior assets of a FPGA bit comprise of a grid of configurable logicsquares ( Clbs ) encompassed by an outskirts of I/O pieces. Indexs are directed inside the FPGA grid by programmable interconnect switches and wire classs.

2.1.1 Need of FPGAs:

By the early 1980 's extended graduated table coordinated circuits ( LSI ) structured the spinal column of a big part of the logiccircuits in important models. Chip, transport/IO accountants, model redstem storksbills and so on were actualized utilizing integrated circuit industry invention. Irregular `` paste principle '' or interconnects were still needed to assist fall in the huge integrated circuits to:

- Produce world-wide control marks ( for resets and so forth. )

- Information marks get downing with one subsystem so onto the following bomber model.

Systems normally comprised of few huge graduated table coordinated parts and extended figure of SSI ( small graduated table incorporated circuit ) and MSI ( average graduated table incorporated circuit ) components.intial enterprise to take attention of this issue prompted betterment of Custom Ics which were to replace the expansive step of interconnect. This reduced model elaborateness and piecing cost, and enhanced executing. Then once more, usage Ics have their ain peculiar hinderances. They are by and large highly extortionate to make, and delay acquainted for point with concern sector ( clip to market ) in visible radiation of expanded lineation clip. There are two kinds of disbursals included being developed of usage Ics

- Expense of promotion and constellation

- Expense of production

( A tradeoff by and large exists between the two disbursals )

Therefore the usage IC methodological analysis was executable for points with high volume, and which were non clip to market delicate. FPGAs were acquainted as an option with usage ICs for realizing whole model on one bit and to give adaptability of reprogram ability to the client. Presentation of FPGAs brought about alteration of thickness in regard to discrete SSI/MSI sections ( inside around 10x of usage ICs ) . An alternate playing point of FPGAs over Custom Ics is that with the aid of machine helped constellation ( CAD ) devices circuits could be executed in a short step of clip ( no physical design transform, no screen devising, no IC piecing ) .

2.2 FPGA Design Flow:

A standout amongst the most imperative focal points of FPGA based lineation is that users can be after it utilizing CAD instruments gave by constellation cybernation organisations. Bland constellation watercourse of a FPGA incorporates wining stairss:

2.2.1 System Design:

At this phase conceiver need to take what section of his utility must be executed on FPGA and how to organize that utility with remainder of the model.

2.2.2 I/O integrating with remainder of the system:

Input Output watercourses of the FPGA are coordinated with remainder of the Printed Circuit Board, which permits the lineation of the PCB quickly in constellation procedure. FPGA merchandisers give extra cybernation programming replies for I/O outline procedure.

2.2.3 Design Description:

Designer depicts outline usefulness either by using conventional editors or by using one of the different Hardware Description Languages ( HDLs ) like Verilog or VHDL.

2.2.4 Synthesis:

Once lineation has been characterized CAD instruments are utilized to put to death the constellation on a given FPGA. Amalgamation incorporates bland promotion, slack promotions, power betterments took after by agreement and directing. Use incorporates Partition, Place and class. The output of constellation executing phase is bit-stream papers.

2.2.5 Design Confirmation:

Bit stream papers is bolstered to a trial system which reenacts the constellation utility and studies faux pass in desired behavior of the lineation. Timing instruments are utilised to concentrate greatest clock return of the constellation. Soon the lineation is stacking onto the mark FPGA appliance and testing is carried out in nature 's sod.

2.2.6 Hardware design and development:

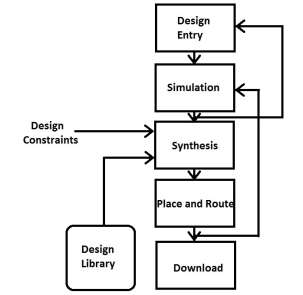

The general methodological analysis of adjustments betterment for programmable logicis demonstrated in Fig. 2.1 and depicted in the subdivisions that take after. Possibly the most dramatic differentiation between equipment and scheduling lineation is the manner an applied scientist must chew over the issue. Programing applied scientists have a inclination to believe in turn, really when they are making a multithreaded requisition. The lines of beginning codification that they compose are invariably executed in a specific order, at any rate inside a given twine. On the off opportunity that there is a working model it is utilised to do the visual aspect of correspondence, yet there is still merely one executing motor. Throughout outline entryway, equipment fashioners must think-and system in analogue. The greater portion of the info indexs are transformed in analogue, as they go through a set of executing motors each one of an agreement of macrocells and interconnections-to their end output marks.

Fig 2.1: Programmable Logic Design Process

Normally, the constellation entryway measure is taken after or assorted with times of utile reenactment. That is the topographic point a trial system is utilized to put to death the lineation and affirm that the right outputs are processed for a given set of trial inputs. Despite the fact that issues with the size or timing of the equipment may at present manifest subsequently, the Godhead can at any rate make certain that his logicis practically right before go oning to the undermentioned stage of betterment.

Gathering merely starts after a practically right representation of the equipment exists. This fittings agreement comprises of two alone stairss. First and first, a center of the route representation of the equipment lineation is generated. This measure is called combination and the consequence is a representation called a netlist. The netlist is gadget independent, so its substance do n't trust on upon the specifics of the FPGA or CPLD ; it is by and large put away in a standard organisation called the Electronic Design Interchange Format ( EDIF ) .

The 2nd venture in the reading methodological analysis is called topographic point & A ; class. This measure includes mapping the consistent constructions depicted in the netlist onto existent macrocells, interconnectednesss, and include and yield pins. This process is like the relative venture in the betterment of a printed circuit board, and it might likewise take into history either programmed or manual design sweetenings. The effect of the topographic point & A ; class procedure is a bitstream. This name is utilised blandly, irrespective of the manner that every CPLD or FPGA ( or household ) has its ain, typically sole, bitstream group. Suffice it to state that the bitstream is the mated information that must be stacked into the FPGA or CPLD to do that bit to put to death a specific adjustments lineation.

Increasingly there are to boot debuggers accessible that at any rate take into consideration single-venturing the equipment program as it executes in the programmable logicgadget. Anyway those merely supplement a reenactment environment that can use a per centum of the information created throughout the topographic point & A ; class venture to give door degree diversion. Clearly, this kind of incorporation of appliance peculiar informations into a nonexclusive trial system obliges a great working relationship between the bit and reproduction setup Sellerss.

Cite this Page

Field Programmable Gate Arrays and Applications. (2018, Sep 03). Retrieved from https://phdessay.com/field-programmable-gate-arrays-and-applications/

Run a free check or have your essay done for you